# Distributed Electrothermal Modeling in VHDL-AMS

Pavel V. Nikitin, Erik Normark, and C.-J. Richard Shi Department of Electrical Engineering University of Washington Seattle, WA 98195-2500, USA. Email: {nikitin, ecn1, cjshi}@ee.washington.edu

Abstract—This paper demonstrates how to apply VHDL-AMS to modeling a coupled distributed electrothermal problem. We present an example of a simple system where two resistors on top of a silicon substrate are thermally coupled. Thermal exchange is described with a heat balance equation discretized and solved using finite difference method. The entire system is modeled in VHDL-AMS. Our work is a tutorial demonstration of VHDL-AMS capability to model coupled electrothermal systems beyond the traditional equivalent thermal network representation. \(^1\)

### I. INTRODUCTION

A general thermal problem can be modeled by using an appropriate simulator that provides a numerical solution of the heat balance (or thermal diffusion) equation for a given set of geometry, sources, and boundary conditions [1]. Modeling a coupled electrothermal problem is more challenging due to the interaction between electrical devices and thermal processes.

Necessity to carry out a concurrent circuit simulation leads to coupling of a thermal simulator and a circuit simulator [2], [3]. A good example of such work can be found in [4], [5]. An alternative approach is to use an equivalent thermal network that consists of sources, capacitors, and resistors. These elements represent the effects of heatflow, self-heating, and mutual coupling between electrothermal devices that dissipate power or are sensitive to temperature. In this approach, the number of variables is drastically reduced. However, since all other thermal effects are reduced to equivalent thermal network representation [6], only the temperature at some spatial points can be found.

While in many cases the second approach provides an adequate accuracy, reducing a 3-D thermal problem to an equivalent thermal circuit network of reasonable size is not trivial, especially for complex systems. At the same time, in the first approach, the process of connecting two simulators is challenging and custom in each case due to the lack of commonly accepted modeling environment. The fact that the time scales for thermal and electric processes are usually quite different presents an additional difficulty in coordinating the operation and interaction of circuit and thermal simulators.

<sup>1</sup>This research was supported by DARPA NeoCAD Program under Grant No. N66001-01-8920 and NSF CAREER Award under Grant No. 9985507

0-7803-8135-1/\$17.00 © 2003 IEEE

VHDL-AMS (an IEEE standard hardware description language [7]) is an example of the natural environment where modeling coupled electrothermal problems becomes straightforward. A thermal node can be added to any element in the circuit. Two quantities associated with each thermal node, temperature and heatflow, adequately describe electrothermal effects of the device. Thermal nodes of various elements are plugged into the thermal environment. The heat exchange can be modeled either using an equivalent thermal network or by solving the heat balance equation in the volume of interest.

Due to the fact that VHDL-AMS multi-physics capability is currently limited to differential and algebraic equations (DAE's) or equivalent circuits [8], an equivalent thermal network method remains the most popular approach for VHDL-AMS modeling of electrothermal problems. Representative works using this approach (also referred to as thermal impedance matrix approach [9]) include modeling of MMIC array [10], MOST transistor [11], self-heating diode [12], and resistor [13].

Up to date, there has been little work related to distributed electrothermal modeling in VHDL-AMS because of the lack of support for partial differential equations (PDE's) in the current language standard [14]. For example, [15] deals only with a 2-D thermal problem without any electrical circuits.

In this paper, we present an example of a distributed problem: a simple circuit where two resistors are electrically independent but thermally coupled via a silicon substrate. Both resistors dissipate power and are sensitive to temperature changes. Thermal exchange is described with a 2-D heat balance equation solved using a finite difference spatial discretization method, similar to [16], where a fully coupled 3-D electrothermal simulation has been carried in MAST language using SABER<sup>2</sup> This approach can also been applied to modeling PDE's in VHDL-AMS [17]. The entire system in our example is modeled purely in VHDL-AMS using freely available simulator Hamster<sup>3</sup>.

The remainder of the paper is organized as follows. Sections II and III present an example and describe thermal modeling. VHDL-AMS implementation is presented in Section IV. Sections V and VI contain results and discussion. Conclusions are given in Section VII.

<sup>&</sup>lt;sup>2</sup>SABER is a trademark of Synopsys Inc.

<sup>&</sup>lt;sup>3</sup>Hamster is now part of Simplorer, trademark of Ansoft Corp.

### II. EXAMPLE

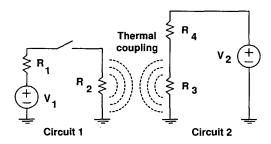

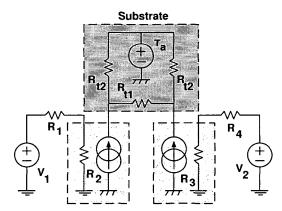

Consider a simple circuit system shown in Fig. 1. The system consists of two circuits, which are decoupled electrically but coupled thermally due to the fact that both  $R_2$  and  $R_3$  are located on the same silicon substrate. Circuit 1 can represent a trigger line in the digital part of a mixed-signal system whereas circuit 2 can represent a transistor amplifier biasing circuit in the analog part of a mixed-signal system.

Fig. 1. Example of a circuit system with electrothermal coupling.

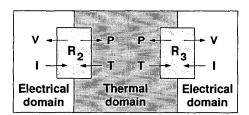

The electrothermal interaction that takes place in this system is illustrated in Fig. 2, where P is dissipated power, T is temperature, I is current, and V is voltage. Other devices are either not temperature sensitive, dissipate negligent power, or located off-chip. For electrothermal

Fig. 2. Electrothermal interaction in the system shown in Fig. 1.

resistors  $R_2$  and  $R_3$ , we will assume that their resistance is given by the following function of temperature [13]:

$$R = R_o \left[ 1 + \alpha (T_r - T_o) \right], \tag{1}$$

where  $R_o$  is the nominal resistance at a normal temperature of  $T_o = 300$  K,  $T_r$  is the resistor temperature, and  $\alpha$  is the temperature coefficient of resistance.

While the example presented here is rather trivial and somewhat artificial, it is a good conceptual demonstration of distributed electrothermal modeling in VHDL-AMS. We intentionally keep it simple to demonstrate clearly all steps involved into application of VHDL-AMS to an electrothermal problem. More complicated examples that include electrothermal semiconductor devices (capacitors, diodes, or transistors) and complex 3-D geometries but can be treated in a similar fashion.

## III. THERMAL MODELING

## A. Geometry

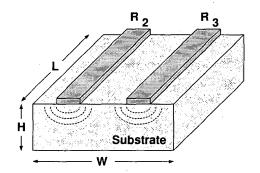

Consider a rectangular substrate shown in Fig. 3 with two resistors  $R_2$  and  $R_3$  located on top of it. The width of the substrate is W, and the height of the substrate is H. Both resistors dissipate power and generate heat

Fig. 3. Geometry of the thermal problem: resistors on top of a substrate.

flux into the substrate. The currents through these resistors depend on their temperatures and change as the substrate temperature changes.

Note that if the resistor length L is much greater than their width and mutual separation, this 3-D problem can be treated as 2-D.

### B. Heat Balance Equation

Assuming that no heat is generated inside the substrate material, the temperature T inside the substrate can be found using the following heat balance equation:

$$\rho C \frac{\partial T}{\partial t} = \vec{\nabla} \cdot \left( k \vec{\nabla} T \right) , \qquad (2)$$

where  $\rho$  is the material density, C is the specific heat capacity, and k is the thermal conductivity.

Assume that the substrate material is uniform, and its properties are temperature-independent. Then we can rewrite (2) in Cartesian coordinates as:

$$\frac{\partial T}{\partial t} = \frac{k}{\rho C} \left( \frac{\partial^2 T}{\partial x^2} + \frac{\partial^2 T}{\partial y^2} \right) \,, \tag{3}$$

where x and y are the transversal coordinates.

Boundary conditions on conductive boundary (contact surfaces between the substrate and resistors) and convective boundary (all other surfaces) are given by [18]:

$$k\frac{\partial T}{\partial \vec{n}} = \begin{cases} \frac{P}{A}, & \text{conductive} \\ h\left(T_a - T\right), & \text{convective} \end{cases} , \tag{4}$$

where  $\vec{n}$  is the vector normal to the boundary surface,  $\vec{P}$  is the power dissipated in a resistor, A is the area occupied by a resistor, and  $T_a$  is the ambient temperature.

#### C. PDE Discretization

A variety of numerical methods are available for solving thermal diffusion PDE'. For simplicity of implementation and clarity of illustration, we use a finite difference discretization with classical central difference formula Since VHDL-AMS does not currently support PDE's, we must discretize partial derivatives with respect to x and y.

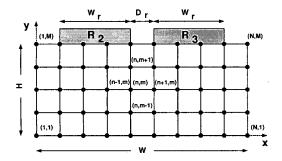

Consider a rectangular  $N \times M$  mesh, whose nodes are the points where the temperature needs to be determined. The mesh and the node labels are shown in Fig. 4. The horizontal and vertical spacings between the mesh points are  $\Delta x = W/(N-1)$  and  $\Delta y = H/(M-1)$ .

Fig. 4. Rectangular finite difference mesh.

Inside the material, (3) can be discretized to obtain:

$$\frac{\partial T}{\partial t} = \frac{k}{\rho C} \left[ \frac{T_{n+1,m} - 2T_{n,m} + T_{n-1,m}}{\Delta x^2} + \frac{T_{n,m+1} - 2T_{n,m} + T_{n,m-1}}{\Delta y^2} \right].$$

(5)

One can rewrite (5) as:

$$\frac{\partial T}{\partial t} = \frac{k}{\rho C \Delta x \Delta y} \times \left[ \frac{T_{n+1,m} - T_{n,m}}{\Delta x} \Delta y - \frac{T_{n,m} - T_{n-1,m}}{\Delta x} \Delta y + \frac{T_{n,m+1} - T_{n,m}}{\Delta y} \Delta x - \frac{T_{n,m} - T_{n,m-1}}{\Delta y} \Delta x \right]. \quad (6)$$

In (6), one can identify inside the brackets several derivative terms which correspond to the horizontal and vertical temperature gradients. To take into account boundary conditions, the derivative terms of (6), which contain mode indices outside of [1..N, 1..M] range are replaced with

$$\pm \frac{h(T_a - T_{n,m})}{k} \tag{7}$$

on convective boundaries or with

$$\pm \frac{P}{kA} \tag{8}$$

on conductive boundaries. The sign (plus or minus) depends on boundary location (left or right, top or bottom).

The discretization described in the previous section results in a system of  $N \times M$  ODE's that can be solved in VHDL-AMS concurrently with the circuit equations. The temperature of each electrothermal resistor is computed by averaging the temperature over all grid points that lie on the resistor contact surface area. Below, we provide VHDL-AMS codes for our circuit system, the electrothermal resistor, and the silicon substrate material.

The values of the circuit elements were chosen such that the thermal coupling effect can be seen in the simulation. These values are:  $V_1=10$  V,  $R_1=10$  Ohm,  $R_2=10$  Ohm (at 300 K),  $V_2=2$  V,  $R_3=10$  Ohm (at 300 K),  $R_4=10$  Ohm. The VHDL-AMS model of the circuit system is shown below.

```

LIBRARY DISCIPLINES; LIBRARY IEEE;

USE DISCIPLINES.ELECTROMAGNETIC_SYSTEM.ALL;

USE DISCIPLINES. THERMAL_SYSTEM. ALL;

USE IEEE.MATH_REAL.ALL;

ENTITY system IS END;

ARCHITECTURE behav OF system IS

TERMINAL n1, n2, n3, n4: ELECTRICAL;

TERMINAL t1, t2: THERMAL;

BEGIN

V1: ENTITY const_source (behav)

GENERIC MAP (2.0)

PORT MAP (nl, electrical ground);

R1: ENTITY resistor

GENERIC MAP (10.0)

PORT MAP (n1, n2);

R2: ENTITY th_resistor

(behav)

GENERIC MAP (10.0,0.1)

PORT MAP (n2, electrical_ground, t1);

R3: ENTITY th_resistor

(behav)

GENERIC MAP (10.0,0.1)

PORT MAP (n3, electrical_ground, t2);

ENTITY resistor

(behav)

GENERIC MAP (10.0)

PORT MAP (n3, n4);

V2: ENTITY pulse_source (behav)

GENERIC MAP (10.0, 25.0e-6, 50.0e-6)

PORT MAP (n4, electrical_ground);

Si: ENTITY material

(behav)

GENERIC MAP (300.0)

PORT MAP (t1,t2);

END behav;

```

The electrothermal resistor model is similar to [13] and is shown below. While in reality the temperature coefficient of resistance is on the order of 0.001-0.01 (CMOS poly and n-well resistors), we chose the value  $\alpha=0.1~\rm K^{-1}$  to display stronger temperature dependence and to emphasize the electrothermal effect.

```

LIBRARY DISCIPLINES; LIBRARY IEEE;

USE DISCIPLINES.ELECTROMAGNETIC_SYSTEM.ALL;

USE DISCIPLINES.THERMAL_SYSTEM.ALL;

USE IEEE.MATH_REAL.ALL;

ENTITY th_resistor IS

GENERIC (r_o, alpha: REAL);

PORT (TERMINAL a, b : ELECTRICAL)

(TERMINAL t: THERMAL);

PORT

END;

ARCHITECTURE behav OF th_resistor IS

QUANTITY v_r ACROSS i_r THROUGH a TO b;

QUANTITY t_r ACROSS h_r THROUGH t

TO thermal_ground;

CONSTANT t_o : REAL := 300.0;

i_r == v_r/(r_o*(1.0+alpha*(t_r - t_o)));

h_r == i_r * v_r;

END behav;

```

The dimensions of the problem geometry were:

$$W=45\,\mathrm{mil}\,, \tag{9}$$

$$H = 20 \,\mathrm{mil}\,,\tag{10}$$

$$L = 150 \,\mathrm{mil}\,,\tag{11}$$

$$W_r = 15 \,\mathrm{mil}\,,\tag{12}$$

$$D_r = 5 \,\mathrm{mil}\,,\tag{13}$$

where  $W_r$  is resistor width,  $D_r$  is resistor spacing, and 1 mil = 0.0254 mm. The mesh had the dimensions of N =10 and M = 5.

We used the following values for the properties of the silicon substrate and its boundaries:

$$k = 1.412 \left[ \frac{W}{K \cdot cm} \right], \qquad (14)$$

$$\rho = 2.33 \left[ \frac{g}{cm^3} \right], \qquad (15)$$

$$\rho = 2.33 \left[ \frac{g}{cm^3} \right] \,, \tag{15}$$

$$C = 0.7 \left[ \frac{J}{g \cdot K} \right], \tag{16}$$

$$C = 0.7 \left[ \frac{J}{g \cdot K} \right], \qquad (16)$$

$$h = 1000 \left[ \frac{W}{cm^2 \cdot K} \right]. \qquad (17)$$

Above, large geometry size and high value of the convective heat transfer coefficient were chosen for illustrative purpose.

Resistor value can be estimated from:

$$R = R_s L/W_r \,, \tag{18}$$

where  $R_s$  is the resistance per square, or sheet resistance. In our example, the sheet resistance was set to be  $R_s =$ 1 Ohm. In reality, sheet resistance in CMOS process would be approximately  $R_s \approx 20$  Ohm for poly and  $R_s \approx$ 2000 Ohm for n-well resistors and the resistor dimensions would be smaller. For example, the size of 200 Ohm poly resistor could be 10  $\mu$ m  $\times$  100  $\mu$ m.

The VHDL-AMS model of the substrate is shown below. Because Hamster simulator does not support simultaneous generate statement, a separate Matlab4 code was used to generate the VHDL-AMS code for the system of equations (6).

```

LIBRARY DISCIPLINES; LIBRARY IEEE;

USE DISCIPLINES.ELECTROMAGNETIC SYSTEM.ALL;

USE DISCIPLINES. THERMAL_SYSTEM. ALL;

USE IEEE.MATH_REAL.ALL;

ENTITY material IS

GENERIC (Ta: REAL);

PORT

(TERMINAL t1, t2: THERMAL);

END:

ARCHITECTURE behav OF material IS

QUANTITY t_1 ACROSS h_1 THROUGH t1

TO thermal_ground;

QUANTITY t_2 ACROSS h_2 THROUGH t2

TO thermal_ground;

CONSTANT k

: REAL := 1.412:

CONSTANT rho

: REAL := 2.33;

: REAL := 0.7:

CONSTANT C

: REAL := 0.001*2.54;

CONSTANT mil

: REAL := 15.0*mil;

CONSTANT Wr

: REAL := 150.0*mil;

CONSTANT L

: REAL := 5.0*mil:

CONSTANT Dr

: REAL := Wr*L;

CONSTANT A1

CONSTANT A2

: REAL := Wr*L;

CONSTANT Width : REAL := 45.0*mil;

CONSTANT Height: REAL := 20.0*mil;

CONSTANT h

REAL := 1000.0;

CONSTANT N

: REAL := 10.0;

CONSTANT M

: REAL := 5.0;

CONSTANT dx

: REAL := Width/(N-1.0);

CONSTANT dy

: REAL := Height/(M-1.0);

CONSTANT Const : REAL := k/(rho*C*dx*dy);

CONSTANT hk

: REAL := h*k;

QUANTITY PkA1, PkA2: REAL;

QUANTITY T11, T12, ... T104, T105:REAL;

BEGIN

BREAK T11 => Ta;

BREAK T105 => Ta;

PkA1 == - h_1 / (k * A1);

PkA2 == - h_2 / (k * A2);

T15'dot==Const*((T25-T15)*dy/dx-dy*hk*

(T15-Ta)+dx*hk*(Ta-T15)-(T15-T14)*dx/dy);

T25' dot == Const* ((T35-T25)*dy/dx-(T25-T15)*

dy/dx+dx*PkA1-(T25-T24)*dx/dy);

T22' dot == Const* ((T32-T22)*dy/dx-(T22-T12)*

dy/dx+(T23-T22)*dx/dy-(T22-T21)*dx/dy);

T101'dot==Const*(dy*hk*(Ta-T101)-(T101-T91)*

dy/dx + (T102-T101) * dx/dy-dx*hk* (Ta-T101));

t_1 == (T25 + T35 + T45 + T55)/4.0;

t_2 == (T65 + T75 + T85 + T95)/4.0;

END behav;

```

<sup>&</sup>lt;sup>4</sup>Trademark of Mathworks, Inc.

#### V. RESULTS

The example presented above was simulated using *Hamster*. The time step was chosen to be 0.1  $\mu$ s to satisfy the stability criterion [19]:

$$\Delta t \le \frac{1}{2} \frac{\rho C}{k} \left( \frac{\Delta x^2 \Delta y^2}{\Delta x^2 + \Delta y^2} \right). \tag{19}$$

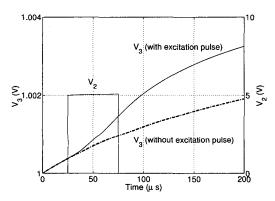

To see the effects of thermal coupling between the two circuits, a 10 V rectangular pulse of 50  $\mu s$  duration was generated by turning switch on at  $t=25~\mu s$  and then off at  $t=75~\mu s$ .

Fig. 5 shows voltages on resistors  $R_2$  and  $R_3$ . In the absence of the excitation pulse from  $V_1$ , as  $V_2$  is turned on at  $t=0~\mu s$ , the voltage on  $R_3$  slowly rises due to self-heating until it reaches an equilibrium. With the pulse, the voltage of 10 V, generated by  $V_1$ , causes initially a voltage of 5 V to appear across  $R_2$ . The current heats  $R_2$  up, causing the rise of its temperature and, respectively, voltage. Generated heat propagates through the substrate to  $R_3$ , increasing its temperature and voltage.

As one can see from Fig. 5, in both cases (with and without excitation pulse) curves for  $V_3$  would look identical until a certain moment of time ( $\approx 30~\mu s$ ), when the heat wave from  $R_2$  reaches  $R_3$ .

Fig. 5. Voltages on resistors  $R_2$  and  $R_3$  as functions of time.

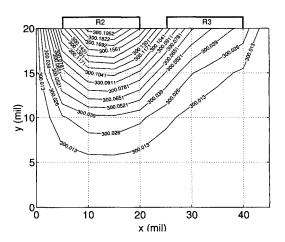

Fig. 6 shows the calculated temperature distribution in the silicon substrate in the vicinity of resistor  $R_3$  at the time moment  $t=200~\mu s$ . Because of the higher current, resistor  $R_2$  dissipates significantly more heat than  $R_3$  and thus defines the temperature distribution inside the substrate.

## VI. DISCUSSION

One can see from Fig. 5 that electrothermal effect in our example is quite small: the change in  $R_3$  voltage caused by it is less than 1%. Semiconductor devices, such as diodes or transistors, typically exhibit much stronger dependence on the temperature and result in more interesting electrothermal behavior.

The example described here can also be modeled with an equivalent thermal network, shown in Fig. 7, where temperature and heatflow play roles of voltage and current (capacitive storage effects are neglected). The heatflow

Fig. 6. Temperature distribution in the substrate at  $t = 200 \ \mu s$ .

of thermal current source associated with electrothermal resistor is equal to the power dissipated in the resistor. A thermal voltage source accounts for the temperature of  $T_a$ . Thermal resistors  $R_{t1}$  and  $R_{t2}$  represent mutual coupling between the resistors  $R_2$  and  $R_3$  and their heat dissipation.

Fig. 7. Equivalent thermal network.

The system shown in Fig. 7 can easily be simulated, if the equivalent thermal resistor values  $R_{t1}$  and  $R_{t2}$  are known. For a large network, extracting those resistances is not trivial [20] and may require an application of model order reduction techniques [18].

In our example, we manually specified the geometry and the material properties, created a mesh, discretized the equations, and set boundary conditions. Ultimately, these tasks need to be automated, as it is done in many domainspecific simulators, such as ANSYS<sup>5</sup> or FEMLAB<sup>6</sup>. One can envision a graphical user interface that allows user to perform these functions for standard IC packages and to generate an appropriate set of VHDL-AMS codes.

Having PDE support in VHDL-AMS [17] would further help to simplify the process of modeling electrothermal problems. For example, with such support, heat balance equation (2) and its boundary conditions for one electrothermal element on top of a substrate could be directly implemented in VHDL-AMS and potentially look as follows:

```

BEGIN pde

T' dot == (k/rho*C)*(T'' dot(x)+T'' dot(y));

END pde;

BEGIN boundary1

T' dot(x) == (\bar{k}*h/(rho*C))*(Ta-T);

T' dot(y) == (k*h/(rho*C))*(Ta-T);

END boundarv1;

BEGIN boundary2

T' dot(y) == k*heatflow/(rho*C*A);

temp == average(T);

END boundary2;

```

where boundary1 is convective boundary, and boundary2 is conductive boundary. Note that boundary conditions for conductive boundary boundary2 include a specification of how an electrothermal element interacts with the substrate, i.e. how quantities heatflow and temp are related to T (function average (T) gives the integrated average of the temperature on the contact surface of electrothermal element).

## VII. CONCLUSIONS

In this paper, we demonstrated how to perform VHDL-AMS modeling of circuit systems with distributed electrothermal interaction. We presented an example where two resistors were thermally coupled via a silicon substrate. The heat balance PDE was discretized using a finite difference method, and the resulting system of ODE's was solved in VHDL-AMS together with the circuit equations using Hamster simulator.

While the example presented here may be simple, it nevertheless proves the concept: complex coupled electrothermal systems can in principle be modeled and simulated in a single unified language environment, such as VHDL-AMS. One major advantage of using the standard language is the fact that the model does not depend on the underlying simulator. This can lead to high portability of electrothermal models and ease of sharing them among the designers.

#### REFERENCES

- [1] T.-Y. Wang and C. C.-P. Chen, "3-D thermal-ADI: a linear-time chip level transient thermal simulator," IEEE Transactions on Computer Aided Design of Integrated Circuits and Systems, vol. 21, pp. 1434-1445, December 2002.

- [2] K. Fukahori and P. R. Gray, "Computer simulation of integrated circuits in the presence of electrothermal interaction," IEEE Journal of Solid-State Circuits, vol. 11, pp. 834–846, December 1976.

- [3] R. K. Williams, M. Rodamaker, and L. Sevilla, "Electrothermal circuit simulation of power ICs combining SPICE and 3D finite element analysis," *Proceedings of the 4th International Symposium* on Power Semiconductor Devices and ICs, pp. 282-287, May 1992.

- [4] L. Sang-Soo and D. J. Allstot, "Electrothermal simulation of integrated circuits," *IEEE Journal of Solid-State Circuits*, vol. 28, p. 1283-1293, December 1993.

- [5] S. Wunsche, C. Clauss, P. Schwarz, and F. Winkler, "Electro-thermal circuit simulation using simulator coupling," IEEE Transactions or Very Large Scale Integration (VLSI) Systems, vol. 5, pp. 277-282, September 1997.

- [6] A. R. Hefner and D. L. Blackburn, "Simulating the dynamic electrothermal behavior of power electronic circuits and systems," *IEEE Transactions on Power Electronics*, vol. 8, pp. 376–385,

- [7] E. Christen and K. Bakalar, "VHDL-AMS a hardware description language for analog and mixed-signal applications," IEEE Trans-actions on Circuits and Systems II: Analog and Digital Signal

- Processing, vol. 46, pp. 1263-1272, October 1999.

[8] B. F. Romanowicz, "Methodology for the modeling and simulation of microsystems," Kluwer Academic Publishers, 1998.

- W. Batty, C. E. Christoffersen, A. J. Panks, S. David, C. M. Snowden, and M. B. Steer, "Electrothermal CAD of power devices and circuits with fully physical time-dependent compact thermal modeling of complex nonlinear 3-d systems," IEEE Transactions on Components and Packaging Technologies, vol. 24, pp. 566-590, December 2001.

- [10] W. Batty, C. E. Christoffersen, A. B. Yakovlev, J. F. Whitaker, A. Mortazawi, A. Al-Zayed, M. Ozkar, S. C. Ortiz, R. M. Reano, K. Yang, L. P. B. Katehi, C. M. Snowden, and M. B. Steer, "Global coupled EM-electrical-thermal simulation and experimental validation for a spatial power combining MMIC array," IEEE Transactions on Microwave Theory and Techniques, vol. 50, pp. 2820-2833, December 2002.

- [11] C. Lallement, F. Pecheux, and Y. Herve, "VHDL-AMS design of a MOST model including deep submicron and thermal-electronic effects," Proceedings of the Fifth IEEE International Workshop on Behavioral Modeling and Simulation, pp. 91-96, 2001.

- [12] L. Starzak, M. Zubert, and A. Napieralski, "The new approach to the power semiconductor devices modeling," *Proceedings of* Fifth International Conference on Modeling and Simulation of Microsystems, pp. 640-644, 2002.

- [13] X. Huang and H. A. Mantooth, "Event-driven electrothermal mod-eling of mixed-signal circuits," Proceedings of IEEE/ACM International Workshop on Behavioral Modeling and Simulation, pp. 10-15. 2000

- [14] C.-J. Shi and A. Vachoux, "VHDL-AMS design objectives and rationale," Current Issues in Electronic Modeling, Kluwer Academic Publishers, vol. 2, pp. 1-30, 1995.

- [15] X. Zhou, B. Liu, and B. Jammes, "Solving steady-state partial differential equation with neural network," Proceedings of 8th International Conference on Neural Information Processing, November

- [16] G. Digele, S. Lindenkreuz, and E. Kasper, "Fully coupled dynamic electro-thermal simulation," IEEE Transactions on Very Large Scale

- Integration (VLSI) Systems, vol. 5, pp. 250–257, September 1997.

[17] P. V. Nikitin, C. J.-R. Shi, and B. Wan, "Modeling partial differential equations in VHDL-AMS," *IEEE SoC Conference*, 2003, in press.

[18] J. T. Hsu and L. Vu-Quoc, "A rational formulation of thermal circuit

- models for electrothermal simulation part I: Finite element method; part II: Model reduction techniques," IEEE Transactions on Circuits and Systems, vol. 43, no. 9, pp. 721-744, 1996.

- [19] M. N. Ozisik, "Finite difference methods in heat transfer," CRC

- Press, 1994.

[20] D. J. Walkey, T. J. Smy, R. G. Dickson, J. S. Brodsky, D. T. Zweidinger, and R. M. Fox, "Equivalent circuit modeling of static substrate thermal coupling using VCVS representation," *IEEE Journal of Solid-State Circuits*, vol. 37, pp. 1198–1206, September 2002.

<sup>&</sup>lt;sup>5</sup>Trademark of ANSYS, Inc.

<sup>&</sup>lt;sup>6</sup>Trademark of The COMSOL Group